栚師

慜

師

栭娫揰柵婍

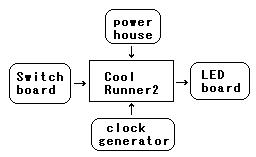

丂CPLD/FPGA傪棙梡偟偰丄栭娫揰柵婍傪嶌惉偟偰傒傑偡丅

丂栭娫揰柵婍偼丄帺摦幵偺杊斊憰抲偱偁傞僀儌價儔僀僓乕傪

丂僀儊乕僕偡傞偲丄傢偐傝傗偡偄偱偟傚偆丅

丂敊慠偲栭娫揰柵婍偲偟偰傕丄愝寁丄奐敪偑偱偒側偄偺偱

丂巇條傪寛傔傑偡丅

- 揹尮揹埑偼丄3.3V偲偡傞

- 係屄偺俴俤俢傪傕偮

- 拫栭偺敾抐偼丄僼僅僩僩儔儞僕僗僞傪棙梡

- 栭偵側傞偲丄係屄偺俴俤俢傪揰柵偡傞

- 揰柵僷僞乕儞偼嵍偐傜塃偵侾屄偢偮揰摂

- 摦嶌僋儘僢僋偼1Hz掱搙偲偡傞

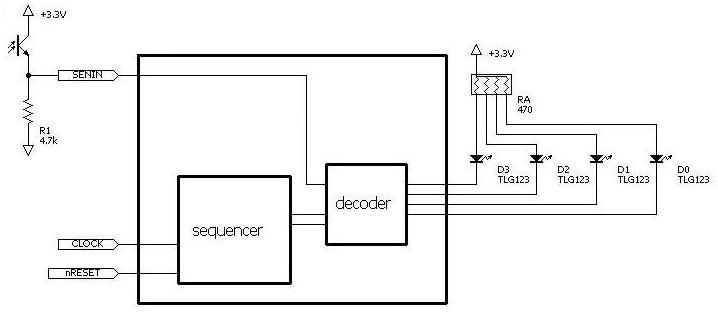

僽儘僢僋恾嶌惉

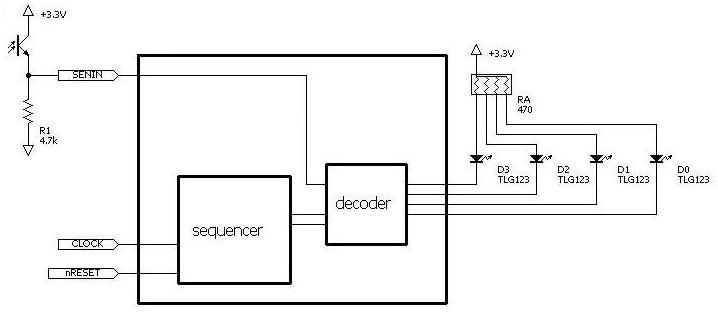

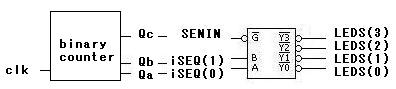

丂巇條偐傜丄僽儘僢僋恾傪嶌惉偟傑偡丅

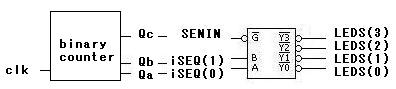

丂僋儘僢僋傪擖椡偟丄僔乕働儞僒偱俀價僢僩偺僐乕僪傪惗惉偟傑偡丅

丂俀價僢僩偺僐乕僪傪僨僐乕僪偟丄俴俤俢偺揰摂怣崋傪嶌惉偟傑偡丅

丂俀價僢僩僐乕僪偲俴俤俢偺揰摂丄徚摂偺娭學傪掕媊偟傑偡丅

丂僋儘僢僋傪擖椡偟丄僔乕働儞僒偱俀價僢僩偺僐乕僪傪惗惉偟傑偡丅

丂俀價僢僩偺僐乕僪傪僨僐乕僪偟丄俴俤俢偺揰摂怣崋傪嶌惉偟傑偡丅

丂俀價僢僩僐乕僪偲俴俤俢偺揰摂丄徚摂偺娭學傪掕媊偟傑偡丅

- (Q1,Q0)=(0,0) -> (LED3,LED2,LED1,LED0)=(ON ,OFF,OFF,OFF)

- (Q1,Q0)=(0,1) -> (LED3,LED2,LED1,LED0)=(OFF,ON ,OFF,OFF)

- (Q1,Q0)=(1,1) -> (LED3,LED2,LED1,LED0)=(OFF,OFF,ON ,OFF)

- (Q1,Q0)=(1,0) -> (LED3,LED2,LED1,LED0)=(OFF,OFF,OFF,ON )

丂僙儞僒乕偐傜偺怣崋偑俴偺偲偒偵丄揰柵偡傞偲偟傑偡丅

丂僙儞僒乕怣崋偑俫偺偲偒丄徚摂偵偡傞偨傔偵丄忦審傪壛偊傑偡丅

- (SENIN,Q1,Q0)=(1,*,*) -> (LED3,LED2,LED1,LED0)=(OFF,OFF,OFF,OFF)

- (SENIN,Q1,Q0)=(0,0,0) -> (LED3,LED2,LED1,LED0)=(ON ,OFF,OFF,OFF)

- (SENIN,Q1,Q0)=(0,0,1) -> (LED3,LED2,LED1,LED0)=(OFF,ON ,OFF,OFF)

- (SENIN,Q1,Q0)=(0,1,1) -> (LED3,LED2,LED1,LED0)=(OFF,OFF,ON ,OFF)

- (SENIN,Q1,Q0)=(0,1,0) -> (LED3,LED2,LED1,LED0)=(OFF,OFF,OFF,ON )

丂僔乕働儞僒偼丄僕儑儞僜儞僇僂儞僞傪峔惉偟丄僋儘僢僋偑偼偄傞搙偵

丂弌椡傪侽仺侾仺俁仺俀仺侽偲孞曉偡偙偲偵偟傑偡丅

丂俴俤俢偵棳偡揹棳偼丄俀倣俙掱搙昁梫側偺偱丄掞峈抣傪寁嶼偟傑偡丅

丂2mA = (3.3V - 2.0V) / R 偐傜丄650兌偵側傝傑偡丅

丂俤24宯楍偱丄彮偟懡偔揹棳傪棳偡曽偑傛偄偺偱丄510兌偐470兌傪

丂巊偄傑偡丅

entity掕媊

丂僽儘僢僋恾偱奜晹偲傗傝偲傝偡傞怣崋偑寛傑傟偽丄entity傪掕媊偟傑偡丅

丂entity偼丄扨弮偵敔偺撪偲奜傪峴偒棃偡傞怣崋傪掕媊偡傟偽傛偄偱偟傚偆丅

entity nflash is

Port (

-- system

nRESET : in std_logic ; -- system reset

CLOCK : in std_logic ; -- reference clock

-- test

SEQOUT : out std_logic_vector(1 downto 0) ;

-- I/O

LEDS : out std_logic_vector(3 downto 0) ;

SENIN : in std_logic --;

);

end nflash;

丂幚嵺偺僠僢僾傪嶌惉屻丄僔乕働儞僒偺摦嶌傪妋擣偡傞偨傔

丂僔乕働儞僒弌椡傪SEQOUT偵愙懕偟傑偡丅

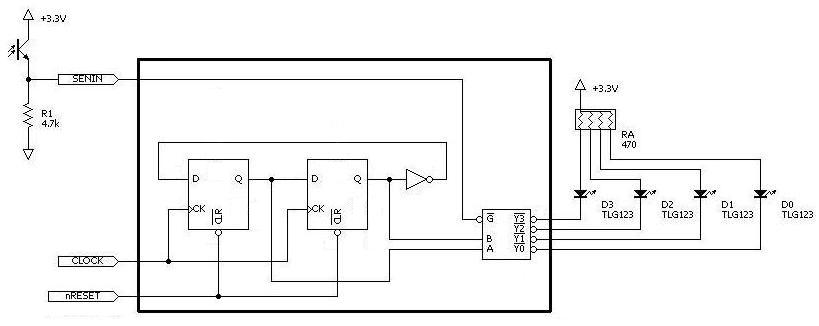

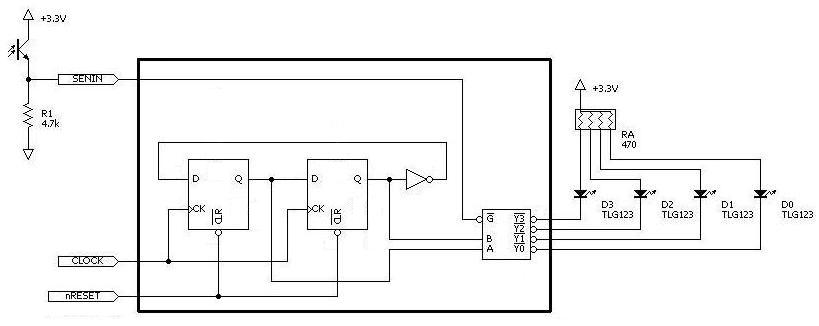

撪晹夞楬専摙

丂僽儘僢僋恾傪嶌惉偟丄僔乕働儞僒偲僨僐乕僟偺摦嶌傪寛掕偟偨偺偱

丂撪晹夞楬傪専摙偟傑偡丅

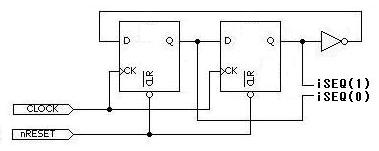

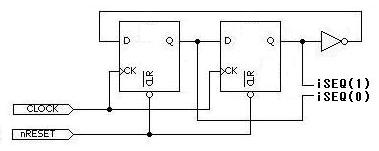

丂僔乕働儞僒偼丄74僔儕乕僘偺俿俿俴僎乕僩偱昞尰偡傞偲丄D僞僀僾

丂僼儕僢僾僼儘僢僾傪2屄巊偭偨2價僢僩僕儑儞僜儞僇僂儞僞偵側傝傑偡丅

丂僔乕働儞僒偼丄74僔儕乕僘偺俿俿俴僎乕僩偱昞尰偡傞偲丄D僞僀僾

丂僼儕僢僾僼儘僢僾傪2屄巊偭偨2價僢僩僕儑儞僜儞僇僂儞僞偵側傝傑偡丅

- previous (Q1,Q0)=(0,0) -> now (Q1,Q0)=(0,1)

- previous (Q1,Q0)=(0,1) -> now (Q1,Q0)=(1,1)

- previous (Q1,Q0)=(1,1) -> now (Q1,Q0)=(1,0)

- previous (Q1,Q0)=(1,0) -> now (Q1,Q0)=(0,0)

丂僕儑儞僜儞僇僂儞僞偼丄僔僼僩儗僕僗僞偺墳梡偱丄嵟廔抜偺

丂弌椡傪斀揮偟丄弶抜偺擖椡偲偡傞偩偗偱峔惉偱偒傑偡丅

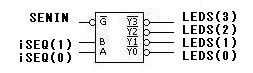

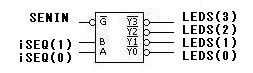

丂僨僐乕僟偼丄74僔儕乕僘偺俿俿俴僎乕僩偱昞尰偡傞偲丄139偺

丂僨僐乕僟偵憡摉偟傑偡丅

- (G,B,A)=(1,0,0) -> (Y3,Y2,Y1,Y0)=(H,H,H,H)

- (G,B,A)=(0,0,0) -> (Y3,Y2,Y1,Y0)=(H,H,H,L)

- (G,B,A)=(0,0,1) -> (Y3,Y2,Y1,Y0)=(H,H,L,H)

- (G,B,A)=(0,1,0) -> (Y3,Y2,Y1,Y0)=(H,L,H,H)

- (G,B,A)=(0,1,1) -> (Y3,Y2,Y1,Y0)=(L,H,H,H)

丂LED偼丄揹棳傪媧崬傔偽傛偄偺偱丄僔乕働儞僒弌椡偵

丂傛傝俴偲側傞傛偆偵偟傑偡丅

僨僐乕僟掕媊

丂僨僐乕僟偼丄扨弮側慻崌偣夞楬側偺偱丄恀棟抣昞傪嶌惉偟偰

丂VHDL偺僐乕僪偵曄姺偟傑偡丅

丂怣崋SENIN偑俴儗儀儖偱丄摦嶌偡傞偺偱丄悧宍偼埲壓偲偟傑偡丅

iLEDS(X) <= '0' when (iSEQ = "??" and SENIN = '0') else '1' ;

丂怣崋LEDS偼丄係價僢僩側偺偱丄僔乕働儞僗弌椡偲寢傃偮偗偰掕媊偟傑偡丅

signal iLEDS : std_logic_vector(3 downto 0);

iLEDS(0) <= '0' when (iSEQ = "00" and SENIN = '0') else '1' ;

iLEDS(1) <= '0' when (iSEQ = "01" and SENIN = '0') else '1' ;

iLEDS(2) <= '0' when (iSEQ = "11" and SENIN = '0') else '1' ;

iLEDS(3) <= '0' when (iSEQ = "10" and SENIN = '0') else '1' ;

LEDS <= iLEDS ;

丂怣崋SENIN偑俴儗儀儖偱丄摦嶌偡傞偺偱丄悧宍偼埲壓偲偟傑偡丅

iLEDS(X) <= '0' when (iSEQ = "??" and SENIN = '0') else '1' ;

丂怣崋LEDS偼丄係價僢僩側偺偱丄僔乕働儞僗弌椡偲寢傃偮偗偰掕媊偟傑偡丅

signal iLEDS : std_logic_vector(3 downto 0);

iLEDS(0) <= '0' when (iSEQ = "00" and SENIN = '0') else '1' ;

iLEDS(1) <= '0' when (iSEQ = "01" and SENIN = '0') else '1' ;

iLEDS(2) <= '0' when (iSEQ = "11" and SENIN = '0') else '1' ;

iLEDS(3) <= '0' when (iSEQ = "10" and SENIN = '0') else '1' ;

LEDS <= iLEDS ;

僨僐乕僟僥僗僩

丂僨僐乕僟傪掕媊偟偨偺偱丄巇條捠傝偺怳晳偄傪偡傞偐傪僥僗僩偟傑偡丅

丂慻崌傢偣夞楬側偺偱丄僇僂儞僞傪梡堄偟偰丄僇僂儞僞偺弌椡傪僨僐乕僟

丂偵愙懕偟傑偡丅僇僂儞僞傪僼儕乕儔儞偝偣丄僨僐乕僟偺弌椡偑偳偆側傞

丂偺偐傪娤應偟傑偡乮慡僷僞乕儞擖椡僥僗僩偵偟傑偡乯丅

丂摦嶌妋擣偑偱偒傟偽傛偄偺偱丄CPLD偺XC9532傪嵹偣偨儃乕僪偵

丂夞楬忣曬傪揮憲偟偰妋擣偟傑偟偨丅僥僗僩梡偺VHDL僐乕僪偼丄

丂埲壓偱偡丅

library IEEE;

use IEEE.STD_LOGIC_1164.ALL;

use IEEE.STD_LOGIC_ARITH.ALL;

use IEEE.STD_LOGIC_UNSIGNED.ALL;

entity tst139 is

port (

-- system

nRESET : in std_logic ;

CLOCK : in std_logic ;

-- test

SENIN : in std_logic ;

ROUT : out std_logic_vector(1 downto 0) ;

LEDS : out std_logic_vector(3 downto 0) --;

) ;

end tst139;

architecture Behavioral of tst139 is

signal iREG : std_logic_vector(1 downto 0) ;

signal iLEDS : std_logic_vector(3 downto 0) ;

begin

-- LEDS

LEDS <= iLEDS ;

iLEDS(0) <= '0' when (iREG = "00" and SENIN = '0') else '1' ;

iLEDS(1) <= '0' when (iREG = "01" and SENIN = '0') else '1' ;

iLEDS(2) <= '0' when (iREG = "11" and SENIN = '0') else '1' ;

iLEDS(3) <= '0' when (iREG = "10" and SENIN = '0') else '1' ;

-- free running counter

process ( nRESET , CLOCK )

begin

if ( nRESET = '0' ) then

iREG <= "00" ;

elsif rising_edge( CLOCK ) then

iREG <= iREG + '1' ;

end if ;

end process ;

ROUT <= iREG ;

end Behavioral;

丂僥僗僩慜偵丄婜懸抣偲寢壥偑斾妑偱偒傞傛偆偵廤寁梡巻偵

婜懸抣傪婰擖偟偰偍偒傑偡丅

丂偙偺応崌偼丄埲壓偲側傝傑偡丅

counter = 000 -> LEDS = 1110 (expected) : ???? (result)

counter = 001 -> LEDS = 1101 (expected) : ???? (result)

counter = 010 -> LEDS = 0111 (expected) : ???? (result)

counter = 011 -> LEDS = 1011 (expected) : ???? (result)

counter = 100 -> LEDS = 1111 (expected) : ???? (result)

counter = 101 -> LEDS = 1111 (expected) : ???? (result)

counter = 110 -> LEDS = 1111 (expected) : ???? (result)

counter = 111 -> LEDS = 1111 (expected) : ???? (result)

丂庤帩偪偺CPLD儃乕僪偼丄僞僀儅乕IC偺555偱2Hz傪敪怳偡傞

丂偺偱丄僼儕乕儔儞僇僂儞僞偺弌椡偲僨僐乕僟偺弌椡偱丄

忋弍偺撪梕偑堦抳偡傞偐傪栚帇僥僗僩偟傑偟偨丅

丂

丂摦嶌妋擣偑偱偒傟偽傛偄偺偱丄CPLD偺XC9532傪嵹偣偨儃乕僪偵

丂夞楬忣曬傪揮憲偟偰妋擣偟傑偟偨丅僥僗僩梡偺VHDL僐乕僪偼丄

丂埲壓偱偡丅

library IEEE;

use IEEE.STD_LOGIC_1164.ALL;

use IEEE.STD_LOGIC_ARITH.ALL;

use IEEE.STD_LOGIC_UNSIGNED.ALL;

entity tst139 is

port (

-- system

nRESET : in std_logic ;

CLOCK : in std_logic ;

-- test

SENIN : in std_logic ;

ROUT : out std_logic_vector(1 downto 0) ;

LEDS : out std_logic_vector(3 downto 0) --;

) ;

end tst139;

architecture Behavioral of tst139 is

signal iREG : std_logic_vector(1 downto 0) ;

signal iLEDS : std_logic_vector(3 downto 0) ;

begin

-- LEDS

LEDS <= iLEDS ;

iLEDS(0) <= '0' when (iREG = "00" and SENIN = '0') else '1' ;

iLEDS(1) <= '0' when (iREG = "01" and SENIN = '0') else '1' ;

iLEDS(2) <= '0' when (iREG = "11" and SENIN = '0') else '1' ;

iLEDS(3) <= '0' when (iREG = "10" and SENIN = '0') else '1' ;

-- free running counter

process ( nRESET , CLOCK )

begin

if ( nRESET = '0' ) then

iREG <= "00" ;

elsif rising_edge( CLOCK ) then

iREG <= iREG + '1' ;

end if ;

end process ;

ROUT <= iREG ;

end Behavioral;

丂僥僗僩慜偵丄婜懸抣偲寢壥偑斾妑偱偒傞傛偆偵廤寁梡巻偵

婜懸抣傪婰擖偟偰偍偒傑偡丅

丂偙偺応崌偼丄埲壓偲側傝傑偡丅

counter = 000 -> LEDS = 1110 (expected) : ???? (result)

counter = 001 -> LEDS = 1101 (expected) : ???? (result)

counter = 010 -> LEDS = 0111 (expected) : ???? (result)

counter = 011 -> LEDS = 1011 (expected) : ???? (result)

counter = 100 -> LEDS = 1111 (expected) : ???? (result)

counter = 101 -> LEDS = 1111 (expected) : ???? (result)

counter = 110 -> LEDS = 1111 (expected) : ???? (result)

counter = 111 -> LEDS = 1111 (expected) : ???? (result)

丂庤帩偪偺CPLD儃乕僪偼丄僞僀儅乕IC偺555偱2Hz傪敪怳偡傞

丂偺偱丄僼儕乕儔儞僇僂儞僞偺弌椡偲僨僐乕僟偺弌椡偱丄

忋弍偺撪梕偑堦抳偡傞偐傪栚帇僥僗僩偟傑偟偨丅

丂

丂寢壥傪婰擖偟偰斾妑偟傑偡丅

counter = 000 -> LEDS = 1110 (expected) : 1110 (result)

counter = 001 -> LEDS = 1101 (expected) : 1101 (result)

counter = 010 -> LEDS = 0111 (expected) : 0111 (result)

counter = 011 -> LEDS = 1011 (expected) : 1011 (result)

counter = 100 -> LEDS = 1111 (expected) : 1111 (result)

counter = 101 -> LEDS = 1111 (expected) : 1111 (result)

counter = 110 -> LEDS = 1111 (expected) : 1111 (result)

counter = 111 -> LEDS = 1111 (expected) : 1111 (result)

丂婜懸抣偲寢壥偑堦抳偟偰偄傞偺偱丄僥僗僩偼廔椆偱偡丅

丂僔儈儏儗乕僞傪摦偐偡傛傝傕丄幚婡偺曽偑僥僗僩偑憗偄応崌傕

丂偁傝丄CPLD/FPGA儃乕僪傪帩偭偰偄傞側傜偽丄専摙偵抣偡傞

僥僗僩曽朄偱偡丅

丂偙偺僥僗僩偺強梫帪娫偼丄僐乕僪嶌惉傪娷傔偰15暘偱偟偨丅

丂偝傜偵丄PeakVHDL偱摦嶌僥僗僩偟傑偟偨丅

丂寢壥傪婰擖偟偰斾妑偟傑偡丅

counter = 000 -> LEDS = 1110 (expected) : 1110 (result)

counter = 001 -> LEDS = 1101 (expected) : 1101 (result)

counter = 010 -> LEDS = 0111 (expected) : 0111 (result)

counter = 011 -> LEDS = 1011 (expected) : 1011 (result)

counter = 100 -> LEDS = 1111 (expected) : 1111 (result)

counter = 101 -> LEDS = 1111 (expected) : 1111 (result)

counter = 110 -> LEDS = 1111 (expected) : 1111 (result)

counter = 111 -> LEDS = 1111 (expected) : 1111 (result)

丂婜懸抣偲寢壥偑堦抳偟偰偄傞偺偱丄僥僗僩偼廔椆偱偡丅

丂僔儈儏儗乕僞傪摦偐偡傛傝傕丄幚婡偺曽偑僥僗僩偑憗偄応崌傕

丂偁傝丄CPLD/FPGA儃乕僪傪帩偭偰偄傞側傜偽丄専摙偵抣偡傞

僥僗僩曽朄偱偡丅

丂偙偺僥僗僩偺強梫帪娫偼丄僐乕僪嶌惉傪娷傔偰15暘偱偟偨丅

丂偝傜偵丄PeakVHDL偱摦嶌僥僗僩偟傑偟偨丅

丂僞僀儈儞僌僠儍乕僩偐傜丄SENIN偑'0'偱丄僨僐乕僪

丂怣崋偑弌椡偝傟偰偄傞偙偲偑傢偐傝傑偡丅

丂僥僗僩梡偺VHDL僐乕僪偼丄埲壓偲偟傑偟偨丅

丂丂library ieee;

丂丂use ieee.std_logic_1164.all;

丂丂use ieee.numeric_std.all;

丂丂use ieee.std_logic_arith.all;

丂丂use std.textio.all;

丂丂use work.TST139;

丂丂entity TESTBNCH is

丂丂end TESTBNCH;

丂丂architecture stimulus of TESTBNCH is

丂丂 component TST139 is

丂丂 port (

丂丂 -- system

丂丂 nRESET : in std_logic ;

丂丂 CLOCK : in std_logic ;

丂丂 -- test

丂丂 SENIN : in std_logic ;

丂丂 ROUT : out std_logic_vector(1 downto 0) ;

丂丂 LEDS : out std_logic_vector(3 downto 0) --;

丂丂 );

丂丂 end component;

丂丂 constant PERIOD : time := 50 ns;

丂丂 constant RPERIOD: time := 70 ns;

丂丂 constant PER0 : time := 125 ns;

丂丂 constant PER1 : time := 175 ns;

丂丂 constant PER2 : time := 255 ns;

丂丂 -- Top level signals go here...

丂丂 signal nRESET : std_logic ;

丂丂 signal CLOCK : std_logic ;

丂丂 signal SENIN : std_logic ;

丂丂 signal ROUT : std_logic_vector(1 downto 0) ;

丂丂 signal LEDS : std_logic_vector(3 downto 0) ;

丂丂 signal done: boolean := false;

丂丂begin

丂丂 DUT: TST139 port map (nRESET,CLOCK,SENIN,ROUT,LEDS);

丂丂 CLOCK1: process

丂丂 variable clktmp: std_ulogic := '0';

丂丂 begin

丂丂 wait for PERIOD/2;

丂丂 clktmp := not clktmp;

丂丂 CLOCK <= clktmp; -- Attach your clock here

丂丂 end process CLOCK1;

丂丂 STIMULUS1: process

丂丂 begin

丂丂 -- Sequential stimulus goes here...

丂丂 --

丂丂 -- Sample stimulus...

丂丂 nRESET <= '0' ; -- Reset the system

丂丂 SENIN <= '0' ;

丂丂 wait for RPERIOD; -- Wait

丂丂 nRESET <= '1' ; -- de-assert reset

丂丂 wait for PER0; -- Wait

丂丂 SENIN <= '1' ;

丂丂 wait for PER1; -- Wait

丂丂 SENIN <= '0' ;

丂丂 wait for PER2; -- Wait

丂丂 SENIN <= '1' ;

丂丂 --

丂丂 -- Enter more stimulus here...

丂丂 --

丂丂 done <= true; -- Turn off the clock

丂丂 wait; -- Suspend simulation

丂丂 end process STIMULUS1;

丂丂end stimulus;

丂摨帪張棟偑壜擻側偙偲傪棙梡偟丄僋儘僢僋偲

丂梌偊傞怣崋傪暘偗偰丄僞僀儈儞僌僠儍乕僩偱

丂堦搙偵僨僐乕僪寢壥傪妋擣偱偒傑偡丅

丂僔僼僩儗僕僗僞偺弌椡偱丄僨僐乕僟偑偳傫側

丂摦嶌傪偡傞偺偐傪妋擣偱偒傑偡丅

丂僞僀儈儞僌僠儍乕僩偐傜丄SENIN偑'0'偱丄僨僐乕僪

丂怣崋偑弌椡偝傟偰偄傞偙偲偑傢偐傝傑偡丅

丂僥僗僩梡偺VHDL僐乕僪偼丄埲壓偲偟傑偟偨丅

丂丂library ieee;

丂丂use ieee.std_logic_1164.all;

丂丂use ieee.numeric_std.all;

丂丂use ieee.std_logic_arith.all;

丂丂use std.textio.all;

丂丂use work.TST139;

丂丂entity TESTBNCH is

丂丂end TESTBNCH;

丂丂architecture stimulus of TESTBNCH is

丂丂 component TST139 is

丂丂 port (

丂丂 -- system

丂丂 nRESET : in std_logic ;

丂丂 CLOCK : in std_logic ;

丂丂 -- test

丂丂 SENIN : in std_logic ;

丂丂 ROUT : out std_logic_vector(1 downto 0) ;

丂丂 LEDS : out std_logic_vector(3 downto 0) --;

丂丂 );

丂丂 end component;

丂丂 constant PERIOD : time := 50 ns;

丂丂 constant RPERIOD: time := 70 ns;

丂丂 constant PER0 : time := 125 ns;

丂丂 constant PER1 : time := 175 ns;

丂丂 constant PER2 : time := 255 ns;

丂丂 -- Top level signals go here...

丂丂 signal nRESET : std_logic ;

丂丂 signal CLOCK : std_logic ;

丂丂 signal SENIN : std_logic ;

丂丂 signal ROUT : std_logic_vector(1 downto 0) ;

丂丂 signal LEDS : std_logic_vector(3 downto 0) ;

丂丂 signal done: boolean := false;

丂丂begin

丂丂 DUT: TST139 port map (nRESET,CLOCK,SENIN,ROUT,LEDS);

丂丂 CLOCK1: process

丂丂 variable clktmp: std_ulogic := '0';

丂丂 begin

丂丂 wait for PERIOD/2;

丂丂 clktmp := not clktmp;

丂丂 CLOCK <= clktmp; -- Attach your clock here

丂丂 end process CLOCK1;

丂丂 STIMULUS1: process

丂丂 begin

丂丂 -- Sequential stimulus goes here...

丂丂 --

丂丂 -- Sample stimulus...

丂丂 nRESET <= '0' ; -- Reset the system

丂丂 SENIN <= '0' ;

丂丂 wait for RPERIOD; -- Wait

丂丂 nRESET <= '1' ; -- de-assert reset

丂丂 wait for PER0; -- Wait

丂丂 SENIN <= '1' ;

丂丂 wait for PER1; -- Wait

丂丂 SENIN <= '0' ;

丂丂 wait for PER2; -- Wait

丂丂 SENIN <= '1' ;

丂丂 --

丂丂 -- Enter more stimulus here...

丂丂 --

丂丂 done <= true; -- Turn off the clock

丂丂 wait; -- Suspend simulation

丂丂 end process STIMULUS1;

丂丂end stimulus;

丂摨帪張棟偑壜擻側偙偲傪棙梡偟丄僋儘僢僋偲

丂梌偊傞怣崋傪暘偗偰丄僞僀儈儞僌僠儍乕僩偱

丂堦搙偵僨僐乕僪寢壥傪妋擣偱偒傑偡丅

丂僔僼僩儗僕僗僞偺弌椡偱丄僨僐乕僟偑偳傫側

丂摦嶌傪偡傞偺偐傪妋擣偱偒傑偡丅

僔乕働儞僒掕媊

丂僔乕働儞僒偼丄撪晹偵僼儕僢僾僼儘僢僾傪傕偮偺偱丄

丂儕僙僢僩帪偵丄弶婜忬懺偑寛傑傞傛偆偵偟傑偡丅

丂儕僙僢僩偼丄摨婜宆偐旕摨婜宆偵側傝傑偡偑丄CPLD偱偺

丂棙梡傕峫偊偰旕摨婜宆偲偟傑偡丅

丂悧宍偼丄process暥偱婰弎偟傑偡丅

丂process ( nRESET , CLOCK )

丂begin

丂丂if ( nRESET = '0' ) then

丂丂丂iSEQ <= "00" ;

丂丂elsif rising_edge( CLOCK ) then

丂丂丂-- ???

丂丂end if ;

丂end process ;

丂僔乕働儞僒偺峔惉偼丄壓恾偺傛偆偵側偭偰偄傞偺偱

丂僔僼僩儗僕僗僞峔惉偵偟丄嵟廔抜偺斀揮抣傪弶抜偺

丂擖椡偵偟傑偡丅

丂process ( nRESET , CLOCK )

丂begin

丂丂if ( nRESET = '0' ) then

丂丂丂iSEQ <= "00" ;

丂丂elsif rising_edge( CLOCK ) then

丂丂丂iSEQ <= iSEQ(0) & (not iSEQ(1)) ;

丂丂end if ;

丂end process ;

丂怣崋傪奜晹偵堷偒弌偟偰丄娤應偱偒傞傛偆偵偟傑偡丅

丂SEQOUT <= iSEQ ;

丂process ( nRESET , CLOCK )

丂begin

丂丂if ( nRESET = '0' ) then

丂丂丂iSEQ <= "00" ;

丂丂elsif rising_edge( CLOCK ) then

丂丂丂iSEQ <= iSEQ(0) & (not iSEQ(1)) ;

丂丂end if ;

丂end process ;

丂怣崋傪奜晹偵堷偒弌偟偰丄娤應偱偒傞傛偆偵偟傑偡丅

丂SEQOUT <= iSEQ ;

僔乕働儞僒僥僗僩

丂僔乕働儞僒傪掕媊偟偨偺偱丄巇條捠傝偺怳晳偄傪偡傞偐傪僥僗僩偟傑偡丅

丂弴彉夞楬側偺偱丄僋儘僢僋偲擖椡抣傪梌偊偰丄弌椡傪娤應偟傑偡丅

丂偙偺僔乕働儞僒偼丄扨弮偵00仺01仺11仺10仺00偲弌椡偟偰偄傞偐傪

丂娤應偡傞偩偗偱廩暘偱偡丅

丂偙偺掱搙偱偁傟偽丄僔儈儏儗乕僞傪巊偆傑偱傕側偔幚婡偵

丂僔乕働儞僒偺撪梕傪揮憲偟偰僥僗僩偟傑偡丅僜乕僗僐乕僪

丂偼丄師偺傛偆偵偟傑偡丅

library IEEE;

use IEEE.STD_LOGIC_1164.ALL;

use IEEE.STD_LOGIC_ARITH.ALL;

use IEEE.STD_LOGIC_UNSIGNED.ALL;

entity tst139s is

Port (

-- system

nRESET : in std_logic;

CLOCK : in std_logic;

-- Johnson counter out

SQOUT : out std_logic_vector(1 downto 0)

);

end tst139s;

architecture Behavioral of tst139s is

signal iSEQ : std_logic_vector(1 downto 0) ;

begin

-- system

process ( nRESET , CLOCK )

begin

if ( nRESET = '0' ) then

iSEQ <= "00" ;

elsif rising_edge( CLOCK ) then

iSEQ <= iSEQ(0) & (not iSEQ(1)) ;

end if ;

end process ;

SQOUT <= iSEQ ;

end Behavioral;

丂僥僗僩慜偵丄婜懸抣偲寢壥偑斾妑偱偒傞傛偆偵廤寁梡巻偵

丂婜懸抣傪婰擖偟偰偍偒傑偡丅

丂偙偺応崌偼丄師偺傛偆偵側傝傑偡丅

reset -> (Q1,Q0) = 00 : ?? (result)

clock (raising edge) -> (Q1,Q0) = 01 : ?? (result)

clock (raising edge) -> (Q1,Q0) = 11 : ?? (result)

clock (raising edge) -> (Q1,Q0) = 10 : ?? (result)

clock (raising edge) -> (Q1,Q0) = 00 : ?? (result)

clock (raising edge) -> (Q1,Q0) = 01 : ?? (result)

丂庤帩偪偺CPLD儃乕僪偼丄僞僀儅乕IC偺555偱俀Hz傪敪怳偡傞

丂偺偱丄CLOCK偵俀Hz傪擖椡偟偰丄栚帇僥僗僩偟傑偡丅

丂寢壥傪婰擖偟偰斾妑偟傑偡丅

reset -> (Q1,Q0) = 00 : 00 (result)

clock (raising edge) -> (Q1,Q0) = 01 : 01 (result)

clock (raising edge) -> (Q1,Q0) = 11 : 11 (result)

clock (raising edge) -> (Q1,Q0) = 10 : 10 (result)

clock (raising edge) -> (Q1,Q0) = 00 : 00 (result)

clock (raising edge) -> (Q1,Q0) = 01 : 01 (result)

丂偝傜偵丄PeakVHDL偱摦嶌僥僗僩偟傑偟偨丅

丂寢壥傪婰擖偟偰斾妑偟傑偡丅

reset -> (Q1,Q0) = 00 : 00 (result)

clock (raising edge) -> (Q1,Q0) = 01 : 01 (result)

clock (raising edge) -> (Q1,Q0) = 11 : 11 (result)

clock (raising edge) -> (Q1,Q0) = 10 : 10 (result)

clock (raising edge) -> (Q1,Q0) = 00 : 00 (result)

clock (raising edge) -> (Q1,Q0) = 01 : 01 (result)

丂偝傜偵丄PeakVHDL偱摦嶌僥僗僩偟傑偟偨丅

丂僞僀儈儞僌僠儍乕僩偐傜丄俀價僢僩偺僕儑儞僜儞僇僂儞僞

丂偵側偭偰偄傞偙偲偑傢偐傝傑偡丅

丂僥僗僩梡偺VHDL僐乕僪偼丄埲壓偲偟傑偟偨丅

丂丂library ieee;

丂丂use ieee.std_logic_1164.all;

丂丂use ieee.numeric_std.all;

丂丂use ieee.std_logic_arith.all;

丂丂use std.textio.all;

丂丂use work.tst139s;

丂丂entity TESTBNCH is

丂丂end TESTBNCH;

丂丂architecture stimulus of TESTBNCH is

丂丂 component tst139s is

丂丂 port (

丂丂 -- system

丂丂 nRESET : in std_logic;

丂丂 CLOCK : in std_logic;

丂丂 -- output

丂丂 SQOUT : out std_logic_vector(1 downto 0) --;

丂丂 );

丂丂 end component;

丂丂 constant PERIOD : time := 50 ns;

丂丂 -- Top level signals go here...

丂丂 signal nRESET : std_logic ;

丂丂 signal CLOCK : std_logic ;

丂丂 signal SQOUT : std_logic_vector(1 downto 0) ;

丂丂 signal done: boolean := false;

丂丂begin

丂丂 DUT: tst139s port map (nRESET,CLOCK,SQOUT);

丂丂 CLOCK1: process

丂丂 variable clktmp: std_ulogic := '0';

丂丂 begin

丂丂 wait for PERIOD/2;

丂丂 clktmp := not clktmp;

丂丂 CLOCK <= clktmp; -- Attach your clock here

丂丂 end process CLOCK1;

丂丂 STIMULUS1: process

丂丂 begin

丂丂 -- Sequential stimulus goes here...

丂丂 --

丂丂 -- Sample stimulus...

丂丂 nRESET <= '0' ; -- Reset the system

丂丂 wait for PERIOD; -- Wait

丂丂 nRESET <= '1' ; -- de-assert reset

丂丂 --

丂丂 -- Enter more stimulus here...

丂丂 --

丂丂 done <= true; -- Turn off the clock

丂丂 wait; -- Suspend simulation

丂丂 end process STIMULUS1;

丂丂end stimulus;

丂僞僀儈儞僌僠儍乕僩偐傜丄俀價僢僩偺僕儑儞僜儞僇僂儞僞

丂偵側偭偰偄傞偙偲偑傢偐傝傑偡丅

丂僥僗僩梡偺VHDL僐乕僪偼丄埲壓偲偟傑偟偨丅

丂丂library ieee;

丂丂use ieee.std_logic_1164.all;

丂丂use ieee.numeric_std.all;

丂丂use ieee.std_logic_arith.all;

丂丂use std.textio.all;

丂丂use work.tst139s;

丂丂entity TESTBNCH is

丂丂end TESTBNCH;

丂丂architecture stimulus of TESTBNCH is

丂丂 component tst139s is

丂丂 port (

丂丂 -- system

丂丂 nRESET : in std_logic;

丂丂 CLOCK : in std_logic;

丂丂 -- output

丂丂 SQOUT : out std_logic_vector(1 downto 0) --;

丂丂 );

丂丂 end component;

丂丂 constant PERIOD : time := 50 ns;

丂丂 -- Top level signals go here...

丂丂 signal nRESET : std_logic ;

丂丂 signal CLOCK : std_logic ;

丂丂 signal SQOUT : std_logic_vector(1 downto 0) ;

丂丂 signal done: boolean := false;

丂丂begin

丂丂 DUT: tst139s port map (nRESET,CLOCK,SQOUT);

丂丂 CLOCK1: process

丂丂 variable clktmp: std_ulogic := '0';

丂丂 begin

丂丂 wait for PERIOD/2;

丂丂 clktmp := not clktmp;

丂丂 CLOCK <= clktmp; -- Attach your clock here

丂丂 end process CLOCK1;

丂丂 STIMULUS1: process

丂丂 begin

丂丂 -- Sequential stimulus goes here...

丂丂 --

丂丂 -- Sample stimulus...

丂丂 nRESET <= '0' ; -- Reset the system

丂丂 wait for PERIOD; -- Wait

丂丂 nRESET <= '1' ; -- de-assert reset

丂丂 --

丂丂 -- Enter more stimulus here...

丂丂 --

丂丂 done <= true; -- Turn off the clock

丂丂 wait; -- Suspend simulation

丂丂 end process STIMULUS1;

丂丂end stimulus;

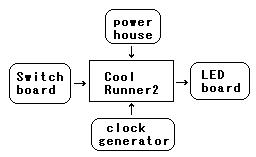

僞乕僎僢僩僠僢僾慖掕

丂偱偒傞尷傝徚旓揹椡傪梷偊偰偍偒偨偄偺偱丄3.3V傪嵟崅揹埑偲偟偰偄傑偡丅

丂3.0V偱偁傟偽丄姡揹抮俀杮偱摦嶌偝偣傜傟傑偡丅

丂嵟嬤偺FPGA偼1.8V掱搙偱傕丄摦嶌偱偒傑偡偑丄LED傪揰摂偝偣傞偵偼

丂2.5V偼傎偟偄偲偙傠偱偡丅CPLD偺拞偱傕丄僆儗儞僕侾屄偺儃儖僞揹抮

偱摦偔CoolRunner2傪棙梡偟傑偡丅

丂CLOCK偲偟偰丄侾俫倸傪憐掕偟傑偟偨偑丄挻掅廃攇傪惗惉偡傞僋儘僢僋

丂僕僃僱儗乕僞偺擖庤惈偑埆偄偺偱丄CPLD/FPGA撪晹偱暘廃偟偨僋儘僢僋

丂傪嶌傞偙偲偵偟傑偡丅

丂侾俫倸傪惗惉偡傞偵偼丄俀偺値忔偱暘廃偡傞偲峫偊傟偽丄侾倠俫倸掱搙

丂傪敪怳婍俬俠偺555偱惗惉偡傞偲偟傑偡丅

丂僔乕働儞僒偱丄係暘廃偟偰偄傞偺偱丄侾倠俫倸傪1024暘廃偡傞偲

丂偡傟偽丄10乮1024暘廃憡摉乯亅2乮4暘廃憡摉乯亖俉價僢僩偺

丂僇僂儞僞傪梡堄偡傟偽廩暘偱偡丅

丂暘廃婍傪掕媊偟傑偡丅

丂signal iCLK : std_logic ;

丂signal iCNT : std_logic_vector(7 downto 0) ;

丂-- system

丂process ( nRESET , CLOCK )

丂begin

丂丂if ( nRESET = '0' ) then

丂丂丂iCNT <= (others => '0') ;

丂丂elsif rising_edge( CLOCK ) then

丂丂丂iCNT <= iCNT + '1' ;

丂丂end if ;

丂end process ;

丂iCLK <= '1' when ( conv_integer(iCNT) = 0 ) else '0' ;

丂僔乕働儞僒偼丄iCLK偱僪儔僀僽偝傟傞傛偆偵嵞掕媊偟傑偡丅

丂-- sequencer

丂process ( nRESET , iCLK )

丂begin

丂丂if ( nRESET = '0' ) then

丂丂丂iSEQ <= "00" ;

丂丂elsif rising_edge( iCLK ) then

丂丂丂iSEQ <= iSEQ(0) & (not iSEQ(1)) ;

丂丂end if ;

丂end process ;

慡僐乕僪

library IEEE;

use IEEE.STD_LOGIC_1164.ALL;

use IEEE.STD_LOGIC_ARITH.ALL;

use IEEE.STD_LOGIC_UNSIGNED.ALL;

entity nflash is

Port (

-- system

nRESET : in std_logic ; -- system reset

CLOCK : in std_logic ; -- reference clock

-- test

SEQOUT : out std_logic_vector(1 downto 0) ;

-- I/O

LEDS : out std_logic_vector(3 downto 0) ;

SENIN : in std_logic --;

);

end nflash;

architecture behavioral of nflash is

signal iCLK : std_logic ;

signal iCNT : std_logic_vector(7 downto 0) ;

signal iSEQ : std_logic_vector(1 downto 0) ;

signal iLEDS: std_logic_vector(3 downto 0) ;

begin

-- system

process ( nRESET , CLOCK )

begin

if ( nRESET = '0' ) then

iCNT <= (others => '0') ;

elsif rising_edge( CLOCK ) then

iCNT <= iCNT + '1' ;

end if ;

end process ;

丂iCLK <= '1' when ( conv_integer(iCNT) = 0 ) else '0' ;

-- sequencer

process ( nRESET , iCLK )

begin

if ( nRESET = '0' ) then

iSEQ <= "00" ;

elsif rising_edge( iCLK ) then

iSEQ <= iSEQ(0) & (not iSEQ(1)) ;

end if ;

end process ;

SEQOUT <= iSEQ ;

-- decoder

LEDS <= iLEDS ;

iLEDS(0) <= '0' when (iSEQ = "00" and SENIN = '0') else '1' ;

iLEDS(1) <= '0' when (iSEQ = "01" and SENIN = '0') else '1' ;

iLEDS(2) <= '0' when (iSEQ = "11" and SENIN = '0') else '1' ;

iLEDS(3) <= '0' when (iSEQ = "10" and SENIN = '0') else '1' ;

end behavioral;

幚婡摦嶌妋擣

丂僔儈儏儗乕僞偱僥僗僩偟丄僠僢僾偵夞楬忣曬傪揮憲偟偨側傜偽姰惉

丂偲偄偆傢偗偵偼偄偒傑偣傫丅幚婡偱摦嶌偡傞偐傪妋擣偟傑偡丅

丂偙偙偱丄儃僞儞僗僀僢僠儃乕僪偲俴俤俢儃乕僪偑昁梫偵側傝傑偡丅

丂SENIN怣崋傪丄儃僞儞偺ON丄OFF偱戙梡偟傑偡丅偙傟偱栭偱側偗傟偽

丂摦嶌妋擣偱偒側偄偲偄偆栤戣偑夝寛偟傑偡丅

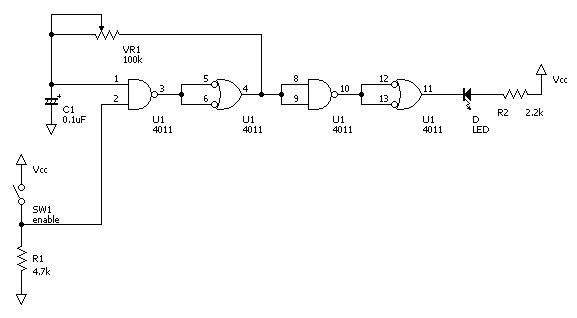

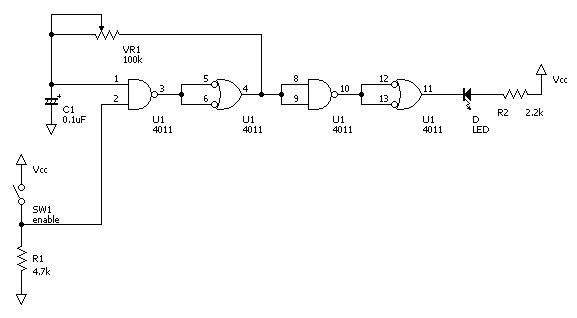

丂僋儘僢僋偼丄壓偺傛偆側夞楬傪嶌惉偟偰懳墳偟傑偡丅僩儕儅乕傪

丂夞偡偲廃攇悢傪曄偊傜傟傑偡丅

丂僋儘僢僋偼丄壓偺傛偆側夞楬傪嶌惉偟偰懳墳偟傑偡丅僩儕儅乕傪

丂夞偡偲廃攇悢傪曄偊傜傟傑偡丅

栚師

慜

師

丂僋儘僢僋傪擖椡偟丄僔乕働儞僒偱俀價僢僩偺僐乕僪傪惗惉偟傑偡丅

丂俀價僢僩偺僐乕僪傪僨僐乕僪偟丄俴俤俢偺揰摂怣崋傪嶌惉偟傑偡丅

丂俀價僢僩僐乕僪偲俴俤俢偺揰摂丄徚摂偺娭學傪掕媊偟傑偡丅

丂僋儘僢僋傪擖椡偟丄僔乕働儞僒偱俀價僢僩偺僐乕僪傪惗惉偟傑偡丅

丂俀價僢僩偺僐乕僪傪僨僐乕僪偟丄俴俤俢偺揰摂怣崋傪嶌惉偟傑偡丅

丂俀價僢僩僐乕僪偲俴俤俢偺揰摂丄徚摂偺娭學傪掕媊偟傑偡丅

丂僔乕働儞僒偼丄74僔儕乕僘偺俿俿俴僎乕僩偱昞尰偡傞偲丄D僞僀僾

丂僼儕僢僾僼儘僢僾傪2屄巊偭偨2價僢僩僕儑儞僜儞僇僂儞僞偵側傝傑偡丅

丂僔乕働儞僒偼丄74僔儕乕僘偺俿俿俴僎乕僩偱昞尰偡傞偲丄D僞僀僾

丂僼儕僢僾僼儘僢僾傪2屄巊偭偨2價僢僩僕儑儞僜儞僇僂儞僞偵側傝傑偡丅

丂怣崋SENIN偑俴儗儀儖偱丄摦嶌偡傞偺偱丄悧宍偼埲壓偲偟傑偡丅

iLEDS(X) <= '0' when (iSEQ = "??" and SENIN = '0') else '1' ;

丂怣崋LEDS偼丄係價僢僩側偺偱丄僔乕働儞僗弌椡偲寢傃偮偗偰掕媊偟傑偡丅

signal iLEDS : std_logic_vector(3 downto 0);

iLEDS(0) <= '0' when (iSEQ = "00" and SENIN = '0') else '1' ;

iLEDS(1) <= '0' when (iSEQ = "01" and SENIN = '0') else '1' ;

iLEDS(2) <= '0' when (iSEQ = "11" and SENIN = '0') else '1' ;

iLEDS(3) <= '0' when (iSEQ = "10" and SENIN = '0') else '1' ;

LEDS <= iLEDS ;

丂怣崋SENIN偑俴儗儀儖偱丄摦嶌偡傞偺偱丄悧宍偼埲壓偲偟傑偡丅

iLEDS(X) <= '0' when (iSEQ = "??" and SENIN = '0') else '1' ;

丂怣崋LEDS偼丄係價僢僩側偺偱丄僔乕働儞僗弌椡偲寢傃偮偗偰掕媊偟傑偡丅

signal iLEDS : std_logic_vector(3 downto 0);

iLEDS(0) <= '0' when (iSEQ = "00" and SENIN = '0') else '1' ;

iLEDS(1) <= '0' when (iSEQ = "01" and SENIN = '0') else '1' ;

iLEDS(2) <= '0' when (iSEQ = "11" and SENIN = '0') else '1' ;

iLEDS(3) <= '0' when (iSEQ = "10" and SENIN = '0') else '1' ;

LEDS <= iLEDS ;

丂摦嶌妋擣偑偱偒傟偽傛偄偺偱丄CPLD偺XC9532傪嵹偣偨儃乕僪偵

丂夞楬忣曬傪揮憲偟偰妋擣偟傑偟偨丅僥僗僩梡偺VHDL僐乕僪偼丄

丂埲壓偱偡丅

library IEEE;

use IEEE.STD_LOGIC_1164.ALL;

use IEEE.STD_LOGIC_ARITH.ALL;

use IEEE.STD_LOGIC_UNSIGNED.ALL;

entity tst139 is

port (

-- system

nRESET : in std_logic ;

CLOCK : in std_logic ;

-- test

SENIN : in std_logic ;

ROUT : out std_logic_vector(1 downto 0) ;

LEDS : out std_logic_vector(3 downto 0) --;

) ;

end tst139;

architecture Behavioral of tst139 is

signal iREG : std_logic_vector(1 downto 0) ;

signal iLEDS : std_logic_vector(3 downto 0) ;

begin

-- LEDS

LEDS <= iLEDS ;

iLEDS(0) <= '0' when (iREG = "00" and SENIN = '0') else '1' ;

iLEDS(1) <= '0' when (iREG = "01" and SENIN = '0') else '1' ;

iLEDS(2) <= '0' when (iREG = "11" and SENIN = '0') else '1' ;

iLEDS(3) <= '0' when (iREG = "10" and SENIN = '0') else '1' ;

-- free running counter

process ( nRESET , CLOCK )

begin

if ( nRESET = '0' ) then

iREG <= "00" ;

elsif rising_edge( CLOCK ) then

iREG <= iREG + '1' ;

end if ;

end process ;

ROUT <= iREG ;

end Behavioral;

丂僥僗僩慜偵丄婜懸抣偲寢壥偑斾妑偱偒傞傛偆偵廤寁梡巻偵

婜懸抣傪婰擖偟偰偍偒傑偡丅

丂偙偺応崌偼丄埲壓偲側傝傑偡丅

counter = 000 -> LEDS = 1110 (expected) : ???? (result)

counter = 001 -> LEDS = 1101 (expected) : ???? (result)

counter = 010 -> LEDS = 0111 (expected) : ???? (result)

counter = 011 -> LEDS = 1011 (expected) : ???? (result)

counter = 100 -> LEDS = 1111 (expected) : ???? (result)

counter = 101 -> LEDS = 1111 (expected) : ???? (result)

counter = 110 -> LEDS = 1111 (expected) : ???? (result)

counter = 111 -> LEDS = 1111 (expected) : ???? (result)

丂庤帩偪偺CPLD儃乕僪偼丄僞僀儅乕IC偺555偱2Hz傪敪怳偡傞

丂偺偱丄僼儕乕儔儞僇僂儞僞偺弌椡偲僨僐乕僟偺弌椡偱丄

忋弍偺撪梕偑堦抳偡傞偐傪栚帇僥僗僩偟傑偟偨丅

丂

丂摦嶌妋擣偑偱偒傟偽傛偄偺偱丄CPLD偺XC9532傪嵹偣偨儃乕僪偵

丂夞楬忣曬傪揮憲偟偰妋擣偟傑偟偨丅僥僗僩梡偺VHDL僐乕僪偼丄

丂埲壓偱偡丅

library IEEE;

use IEEE.STD_LOGIC_1164.ALL;

use IEEE.STD_LOGIC_ARITH.ALL;

use IEEE.STD_LOGIC_UNSIGNED.ALL;

entity tst139 is

port (

-- system

nRESET : in std_logic ;

CLOCK : in std_logic ;

-- test

SENIN : in std_logic ;

ROUT : out std_logic_vector(1 downto 0) ;

LEDS : out std_logic_vector(3 downto 0) --;

) ;

end tst139;

architecture Behavioral of tst139 is

signal iREG : std_logic_vector(1 downto 0) ;

signal iLEDS : std_logic_vector(3 downto 0) ;

begin

-- LEDS

LEDS <= iLEDS ;

iLEDS(0) <= '0' when (iREG = "00" and SENIN = '0') else '1' ;

iLEDS(1) <= '0' when (iREG = "01" and SENIN = '0') else '1' ;

iLEDS(2) <= '0' when (iREG = "11" and SENIN = '0') else '1' ;

iLEDS(3) <= '0' when (iREG = "10" and SENIN = '0') else '1' ;

-- free running counter

process ( nRESET , CLOCK )

begin

if ( nRESET = '0' ) then

iREG <= "00" ;

elsif rising_edge( CLOCK ) then

iREG <= iREG + '1' ;

end if ;

end process ;

ROUT <= iREG ;

end Behavioral;

丂僥僗僩慜偵丄婜懸抣偲寢壥偑斾妑偱偒傞傛偆偵廤寁梡巻偵

婜懸抣傪婰擖偟偰偍偒傑偡丅

丂偙偺応崌偼丄埲壓偲側傝傑偡丅

counter = 000 -> LEDS = 1110 (expected) : ???? (result)

counter = 001 -> LEDS = 1101 (expected) : ???? (result)

counter = 010 -> LEDS = 0111 (expected) : ???? (result)

counter = 011 -> LEDS = 1011 (expected) : ???? (result)

counter = 100 -> LEDS = 1111 (expected) : ???? (result)

counter = 101 -> LEDS = 1111 (expected) : ???? (result)

counter = 110 -> LEDS = 1111 (expected) : ???? (result)

counter = 111 -> LEDS = 1111 (expected) : ???? (result)

丂庤帩偪偺CPLD儃乕僪偼丄僞僀儅乕IC偺555偱2Hz傪敪怳偡傞

丂偺偱丄僼儕乕儔儞僇僂儞僞偺弌椡偲僨僐乕僟偺弌椡偱丄

忋弍偺撪梕偑堦抳偡傞偐傪栚帇僥僗僩偟傑偟偨丅

丂

丂寢壥傪婰擖偟偰斾妑偟傑偡丅

counter = 000 -> LEDS = 1110 (expected) : 1110 (result)

counter = 001 -> LEDS = 1101 (expected) : 1101 (result)

counter = 010 -> LEDS = 0111 (expected) : 0111 (result)

counter = 011 -> LEDS = 1011 (expected) : 1011 (result)

counter = 100 -> LEDS = 1111 (expected) : 1111 (result)

counter = 101 -> LEDS = 1111 (expected) : 1111 (result)

counter = 110 -> LEDS = 1111 (expected) : 1111 (result)

counter = 111 -> LEDS = 1111 (expected) : 1111 (result)

丂婜懸抣偲寢壥偑堦抳偟偰偄傞偺偱丄僥僗僩偼廔椆偱偡丅

丂僔儈儏儗乕僞傪摦偐偡傛傝傕丄幚婡偺曽偑僥僗僩偑憗偄応崌傕

丂偁傝丄CPLD/FPGA儃乕僪傪帩偭偰偄傞側傜偽丄専摙偵抣偡傞

僥僗僩曽朄偱偡丅

丂偙偺僥僗僩偺強梫帪娫偼丄僐乕僪嶌惉傪娷傔偰15暘偱偟偨丅

丂偝傜偵丄PeakVHDL偱摦嶌僥僗僩偟傑偟偨丅

丂寢壥傪婰擖偟偰斾妑偟傑偡丅

counter = 000 -> LEDS = 1110 (expected) : 1110 (result)

counter = 001 -> LEDS = 1101 (expected) : 1101 (result)

counter = 010 -> LEDS = 0111 (expected) : 0111 (result)

counter = 011 -> LEDS = 1011 (expected) : 1011 (result)

counter = 100 -> LEDS = 1111 (expected) : 1111 (result)

counter = 101 -> LEDS = 1111 (expected) : 1111 (result)

counter = 110 -> LEDS = 1111 (expected) : 1111 (result)

counter = 111 -> LEDS = 1111 (expected) : 1111 (result)

丂婜懸抣偲寢壥偑堦抳偟偰偄傞偺偱丄僥僗僩偼廔椆偱偡丅

丂僔儈儏儗乕僞傪摦偐偡傛傝傕丄幚婡偺曽偑僥僗僩偑憗偄応崌傕

丂偁傝丄CPLD/FPGA儃乕僪傪帩偭偰偄傞側傜偽丄専摙偵抣偡傞

僥僗僩曽朄偱偡丅

丂偙偺僥僗僩偺強梫帪娫偼丄僐乕僪嶌惉傪娷傔偰15暘偱偟偨丅

丂偝傜偵丄PeakVHDL偱摦嶌僥僗僩偟傑偟偨丅

丂僞僀儈儞僌僠儍乕僩偐傜丄SENIN偑'0'偱丄僨僐乕僪

丂怣崋偑弌椡偝傟偰偄傞偙偲偑傢偐傝傑偡丅

丂僥僗僩梡偺VHDL僐乕僪偼丄埲壓偲偟傑偟偨丅

丂丂library ieee;

丂丂use ieee.std_logic_1164.all;

丂丂use ieee.numeric_std.all;

丂丂use ieee.std_logic_arith.all;

丂丂use std.textio.all;

丂丂use work.TST139;

丂丂entity TESTBNCH is

丂丂end TESTBNCH;

丂丂architecture stimulus of TESTBNCH is

丂丂 component TST139 is

丂丂 port (

丂丂 -- system

丂丂 nRESET : in std_logic ;

丂丂 CLOCK : in std_logic ;

丂丂 -- test

丂丂 SENIN : in std_logic ;

丂丂 ROUT : out std_logic_vector(1 downto 0) ;

丂丂 LEDS : out std_logic_vector(3 downto 0) --;

丂丂 );

丂丂 end component;

丂丂 constant PERIOD : time := 50 ns;

丂丂 constant RPERIOD: time := 70 ns;

丂丂 constant PER0 : time := 125 ns;

丂丂 constant PER1 : time := 175 ns;

丂丂 constant PER2 : time := 255 ns;

丂丂 -- Top level signals go here...

丂丂 signal nRESET : std_logic ;

丂丂 signal CLOCK : std_logic ;

丂丂 signal SENIN : std_logic ;

丂丂 signal ROUT : std_logic_vector(1 downto 0) ;

丂丂 signal LEDS : std_logic_vector(3 downto 0) ;

丂丂 signal done: boolean := false;

丂丂begin

丂丂 DUT: TST139 port map (nRESET,CLOCK,SENIN,ROUT,LEDS);

丂丂 CLOCK1: process

丂丂 variable clktmp: std_ulogic := '0';

丂丂 begin

丂丂 wait for PERIOD/2;

丂丂 clktmp := not clktmp;

丂丂 CLOCK <= clktmp; -- Attach your clock here

丂丂 end process CLOCK1;

丂丂 STIMULUS1: process

丂丂 begin

丂丂 -- Sequential stimulus goes here...

丂丂 --

丂丂 -- Sample stimulus...

丂丂 nRESET <= '0' ; -- Reset the system

丂丂 SENIN <= '0' ;

丂丂 wait for RPERIOD; -- Wait

丂丂 nRESET <= '1' ; -- de-assert reset

丂丂 wait for PER0; -- Wait

丂丂 SENIN <= '1' ;

丂丂 wait for PER1; -- Wait

丂丂 SENIN <= '0' ;

丂丂 wait for PER2; -- Wait

丂丂 SENIN <= '1' ;

丂丂 --

丂丂 -- Enter more stimulus here...

丂丂 --

丂丂 done <= true; -- Turn off the clock

丂丂 wait; -- Suspend simulation

丂丂 end process STIMULUS1;

丂丂end stimulus;

丂摨帪張棟偑壜擻側偙偲傪棙梡偟丄僋儘僢僋偲

丂梌偊傞怣崋傪暘偗偰丄僞僀儈儞僌僠儍乕僩偱

丂堦搙偵僨僐乕僪寢壥傪妋擣偱偒傑偡丅

丂僔僼僩儗僕僗僞偺弌椡偱丄僨僐乕僟偑偳傫側

丂摦嶌傪偡傞偺偐傪妋擣偱偒傑偡丅

丂僞僀儈儞僌僠儍乕僩偐傜丄SENIN偑'0'偱丄僨僐乕僪

丂怣崋偑弌椡偝傟偰偄傞偙偲偑傢偐傝傑偡丅

丂僥僗僩梡偺VHDL僐乕僪偼丄埲壓偲偟傑偟偨丅

丂丂library ieee;

丂丂use ieee.std_logic_1164.all;

丂丂use ieee.numeric_std.all;

丂丂use ieee.std_logic_arith.all;

丂丂use std.textio.all;

丂丂use work.TST139;

丂丂entity TESTBNCH is

丂丂end TESTBNCH;

丂丂architecture stimulus of TESTBNCH is

丂丂 component TST139 is

丂丂 port (

丂丂 -- system

丂丂 nRESET : in std_logic ;

丂丂 CLOCK : in std_logic ;

丂丂 -- test

丂丂 SENIN : in std_logic ;

丂丂 ROUT : out std_logic_vector(1 downto 0) ;

丂丂 LEDS : out std_logic_vector(3 downto 0) --;

丂丂 );

丂丂 end component;

丂丂 constant PERIOD : time := 50 ns;

丂丂 constant RPERIOD: time := 70 ns;

丂丂 constant PER0 : time := 125 ns;

丂丂 constant PER1 : time := 175 ns;

丂丂 constant PER2 : time := 255 ns;

丂丂 -- Top level signals go here...

丂丂 signal nRESET : std_logic ;

丂丂 signal CLOCK : std_logic ;

丂丂 signal SENIN : std_logic ;

丂丂 signal ROUT : std_logic_vector(1 downto 0) ;

丂丂 signal LEDS : std_logic_vector(3 downto 0) ;

丂丂 signal done: boolean := false;

丂丂begin

丂丂 DUT: TST139 port map (nRESET,CLOCK,SENIN,ROUT,LEDS);

丂丂 CLOCK1: process

丂丂 variable clktmp: std_ulogic := '0';

丂丂 begin

丂丂 wait for PERIOD/2;

丂丂 clktmp := not clktmp;

丂丂 CLOCK <= clktmp; -- Attach your clock here

丂丂 end process CLOCK1;

丂丂 STIMULUS1: process

丂丂 begin

丂丂 -- Sequential stimulus goes here...

丂丂 --

丂丂 -- Sample stimulus...

丂丂 nRESET <= '0' ; -- Reset the system

丂丂 SENIN <= '0' ;

丂丂 wait for RPERIOD; -- Wait

丂丂 nRESET <= '1' ; -- de-assert reset

丂丂 wait for PER0; -- Wait

丂丂 SENIN <= '1' ;

丂丂 wait for PER1; -- Wait

丂丂 SENIN <= '0' ;

丂丂 wait for PER2; -- Wait

丂丂 SENIN <= '1' ;

丂丂 --

丂丂 -- Enter more stimulus here...

丂丂 --

丂丂 done <= true; -- Turn off the clock

丂丂 wait; -- Suspend simulation

丂丂 end process STIMULUS1;

丂丂end stimulus;

丂摨帪張棟偑壜擻側偙偲傪棙梡偟丄僋儘僢僋偲

丂梌偊傞怣崋傪暘偗偰丄僞僀儈儞僌僠儍乕僩偱

丂堦搙偵僨僐乕僪寢壥傪妋擣偱偒傑偡丅

丂僔僼僩儗僕僗僞偺弌椡偱丄僨僐乕僟偑偳傫側

丂摦嶌傪偡傞偺偐傪妋擣偱偒傑偡丅

丂process ( nRESET , CLOCK )

丂begin

丂丂if ( nRESET = '0' ) then

丂丂丂iSEQ <= "00" ;

丂丂elsif rising_edge( CLOCK ) then

丂丂丂iSEQ <= iSEQ(0) & (not iSEQ(1)) ;

丂丂end if ;

丂end process ;

丂怣崋傪奜晹偵堷偒弌偟偰丄娤應偱偒傞傛偆偵偟傑偡丅

丂SEQOUT <= iSEQ ;

丂process ( nRESET , CLOCK )

丂begin

丂丂if ( nRESET = '0' ) then

丂丂丂iSEQ <= "00" ;

丂丂elsif rising_edge( CLOCK ) then

丂丂丂iSEQ <= iSEQ(0) & (not iSEQ(1)) ;

丂丂end if ;

丂end process ;

丂怣崋傪奜晹偵堷偒弌偟偰丄娤應偱偒傞傛偆偵偟傑偡丅

丂SEQOUT <= iSEQ ;

丂寢壥傪婰擖偟偰斾妑偟傑偡丅

reset -> (Q1,Q0) = 00 : 00 (result)

clock (raising edge) -> (Q1,Q0) = 01 : 01 (result)

clock (raising edge) -> (Q1,Q0) = 11 : 11 (result)

clock (raising edge) -> (Q1,Q0) = 10 : 10 (result)

clock (raising edge) -> (Q1,Q0) = 00 : 00 (result)

clock (raising edge) -> (Q1,Q0) = 01 : 01 (result)

丂偝傜偵丄PeakVHDL偱摦嶌僥僗僩偟傑偟偨丅

丂寢壥傪婰擖偟偰斾妑偟傑偡丅

reset -> (Q1,Q0) = 00 : 00 (result)

clock (raising edge) -> (Q1,Q0) = 01 : 01 (result)

clock (raising edge) -> (Q1,Q0) = 11 : 11 (result)

clock (raising edge) -> (Q1,Q0) = 10 : 10 (result)

clock (raising edge) -> (Q1,Q0) = 00 : 00 (result)

clock (raising edge) -> (Q1,Q0) = 01 : 01 (result)

丂偝傜偵丄PeakVHDL偱摦嶌僥僗僩偟傑偟偨丅

丂僞僀儈儞僌僠儍乕僩偐傜丄俀價僢僩偺僕儑儞僜儞僇僂儞僞

丂偵側偭偰偄傞偙偲偑傢偐傝傑偡丅

丂僥僗僩梡偺VHDL僐乕僪偼丄埲壓偲偟傑偟偨丅

丂丂library ieee;

丂丂use ieee.std_logic_1164.all;

丂丂use ieee.numeric_std.all;

丂丂use ieee.std_logic_arith.all;

丂丂use std.textio.all;

丂丂use work.tst139s;

丂丂entity TESTBNCH is

丂丂end TESTBNCH;

丂丂architecture stimulus of TESTBNCH is

丂丂 component tst139s is

丂丂 port (

丂丂 -- system

丂丂 nRESET : in std_logic;

丂丂 CLOCK : in std_logic;

丂丂 -- output

丂丂 SQOUT : out std_logic_vector(1 downto 0) --;

丂丂 );

丂丂 end component;

丂丂 constant PERIOD : time := 50 ns;

丂丂 -- Top level signals go here...

丂丂 signal nRESET : std_logic ;

丂丂 signal CLOCK : std_logic ;

丂丂 signal SQOUT : std_logic_vector(1 downto 0) ;

丂丂 signal done: boolean := false;

丂丂begin

丂丂 DUT: tst139s port map (nRESET,CLOCK,SQOUT);

丂丂 CLOCK1: process

丂丂 variable clktmp: std_ulogic := '0';

丂丂 begin

丂丂 wait for PERIOD/2;

丂丂 clktmp := not clktmp;

丂丂 CLOCK <= clktmp; -- Attach your clock here

丂丂 end process CLOCK1;

丂丂 STIMULUS1: process

丂丂 begin

丂丂 -- Sequential stimulus goes here...

丂丂 --

丂丂 -- Sample stimulus...

丂丂 nRESET <= '0' ; -- Reset the system

丂丂 wait for PERIOD; -- Wait

丂丂 nRESET <= '1' ; -- de-assert reset

丂丂 --

丂丂 -- Enter more stimulus here...

丂丂 --

丂丂 done <= true; -- Turn off the clock

丂丂 wait; -- Suspend simulation

丂丂 end process STIMULUS1;

丂丂end stimulus;

丂僞僀儈儞僌僠儍乕僩偐傜丄俀價僢僩偺僕儑儞僜儞僇僂儞僞

丂偵側偭偰偄傞偙偲偑傢偐傝傑偡丅

丂僥僗僩梡偺VHDL僐乕僪偼丄埲壓偲偟傑偟偨丅

丂丂library ieee;

丂丂use ieee.std_logic_1164.all;

丂丂use ieee.numeric_std.all;

丂丂use ieee.std_logic_arith.all;

丂丂use std.textio.all;

丂丂use work.tst139s;

丂丂entity TESTBNCH is

丂丂end TESTBNCH;

丂丂architecture stimulus of TESTBNCH is

丂丂 component tst139s is

丂丂 port (

丂丂 -- system

丂丂 nRESET : in std_logic;

丂丂 CLOCK : in std_logic;

丂丂 -- output

丂丂 SQOUT : out std_logic_vector(1 downto 0) --;

丂丂 );

丂丂 end component;

丂丂 constant PERIOD : time := 50 ns;

丂丂 -- Top level signals go here...

丂丂 signal nRESET : std_logic ;

丂丂 signal CLOCK : std_logic ;

丂丂 signal SQOUT : std_logic_vector(1 downto 0) ;

丂丂 signal done: boolean := false;

丂丂begin

丂丂 DUT: tst139s port map (nRESET,CLOCK,SQOUT);

丂丂 CLOCK1: process

丂丂 variable clktmp: std_ulogic := '0';

丂丂 begin

丂丂 wait for PERIOD/2;

丂丂 clktmp := not clktmp;

丂丂 CLOCK <= clktmp; -- Attach your clock here

丂丂 end process CLOCK1;

丂丂 STIMULUS1: process

丂丂 begin

丂丂 -- Sequential stimulus goes here...

丂丂 --

丂丂 -- Sample stimulus...

丂丂 nRESET <= '0' ; -- Reset the system

丂丂 wait for PERIOD; -- Wait

丂丂 nRESET <= '1' ; -- de-assert reset

丂丂 --

丂丂 -- Enter more stimulus here...

丂丂 --

丂丂 done <= true; -- Turn off the clock

丂丂 wait; -- Suspend simulation

丂丂 end process STIMULUS1;

丂丂end stimulus;

丂僋儘僢僋偼丄壓偺傛偆側夞楬傪嶌惉偟偰懳墳偟傑偡丅僩儕儅乕傪

丂夞偡偲廃攇悢傪曄偊傜傟傑偡丅

丂僋儘僢僋偼丄壓偺傛偆側夞楬傪嶌惉偟偰懳墳偟傑偡丅僩儕儅乕傪

丂夞偡偲廃攇悢傪曄偊傜傟傑偡丅