目次

前

次

シンクロナイザ

同期をとるための回路を、シンクロナイザ(Synchronizer)と呼びます。

CPLD/FPGA内部の回路ブロックは、すべて並列に動作しています。

各ブロック間で同期を取るために、トリガーとフラグを利用します。

内部ブロックの同期は、トリガーとフラグでよいのですが、システム

として動くためには、入力と出力が内部ブロックと同期している必要

があります。

入力の同期をとるための回路(入力シンクロナイザ)と出力の同期を

とるための回路(出力シンクロナイザ)について説明します。

入力シンクロナイザ

入力シンクロナイザには、次のような種類があります。

- 入力バッファ

- シリアルーパラレル変換器

- パラレルーシリアル変換器

- FIFO(First In First Out)

- LIFO(Last In First Out)

言葉で表現すると、いろいろな種類があるように見えますが

2パターンに集約されます。

- FIFO(First In First Out)

- LIFO(Last In First Out)

回路でまとめてしまうと、レジスタとシフトレジスタの2種になります。

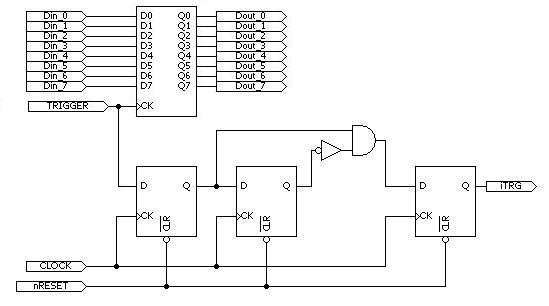

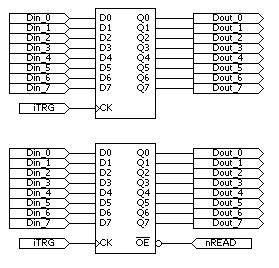

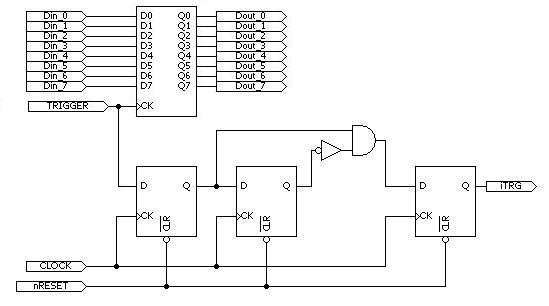

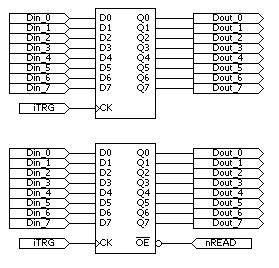

入力バッファ

最も単純な入力バッファは、下図のようにレジスタを用意して

外部トリガーでデータをラッチ(記憶)する回路です。

外部からデータが入力されたことを、RisingEdgeかFallingEdgeのトリガー

で捕捉して、内部回路に信号として伝達します。

process( nRESET , TRIGGER )

begin

if ( nRESET = '0' ) then

iREG <= (others => '0') ;

elsif rising_edge( TRIGGER ) then

iREG <= Din ;

end if ;

end process;

Dout <= iREG ;

process( nRESET , CLOCK )

begin

if ( nRESET = '0' ) then

iSREG <= "00" ;

elsif rising_edge( CLOCK ) then

-- shift register

iSREG <= iSREG(0) & TRIGGER ;

end if ;

end process;

-- judge

iTRG <= '1' when ( iSREG = "01" ) else '0' ;

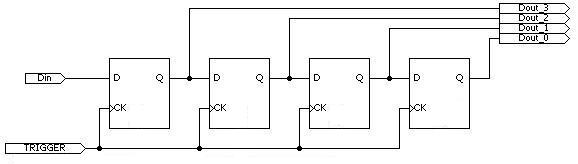

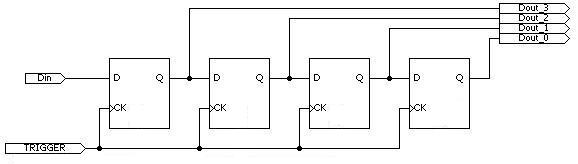

シリアルーパラレル変換器

シリアル-パラレル変換は、シフトレジスタを用意しておき

外部トリガーでデータ入力とシフトを同時に実現します。

外部からデータが入力されたことを、RisingEdgeかFallingEdgeのトリガー

で捕捉して、内部回路に信号として伝達します。

process( nRESET , TRIGGER )

begin

if ( nRESET = '0' ) then

iREG <= (others => '0') ;

elsif rising_edge( TRIGGER ) then

iREG <= Din ;

end if ;

end process;

Dout <= iREG ;

process( nRESET , CLOCK )

begin

if ( nRESET = '0' ) then

iSREG <= "00" ;

elsif rising_edge( CLOCK ) then

-- shift register

iSREG <= iSREG(0) & TRIGGER ;

end if ;

end process;

-- judge

iTRG <= '1' when ( iSREG = "01" ) else '0' ;

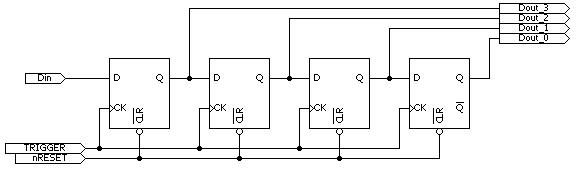

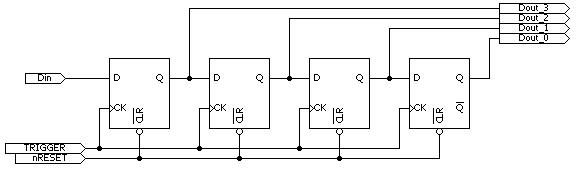

シリアルーパラレル変換器

シリアル-パラレル変換は、シフトレジスタを用意しておき

外部トリガーでデータ入力とシフトを同時に実現します。

全データのセットが終了したかは、データ自体にフラグを用意して

LSBかMSBにつけておくか、もう一つシフトレジスタを用意し

内部回路に信号として伝達します。

process( nRESET , TRIGGER )

begin

if ( nRESET = '0' ) then

iREG <= "0000" ;

elsif rising_edge( TRIGGER ) then

iREG <= iREG(2 downto 0) & Din ;

end if ;

end process;

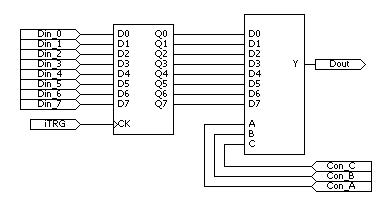

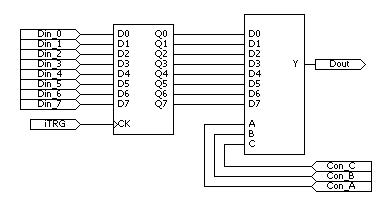

パラレルーシリアル変換器

入力バッファに、データセレクタを接続します。

全データのセットが終了したかは、データ自体にフラグを用意して

LSBかMSBにつけておくか、もう一つシフトレジスタを用意し

内部回路に信号として伝達します。

process( nRESET , TRIGGER )

begin

if ( nRESET = '0' ) then

iREG <= "0000" ;

elsif rising_edge( TRIGGER ) then

iREG <= iREG(2 downto 0) & Din ;

end if ;

end process;

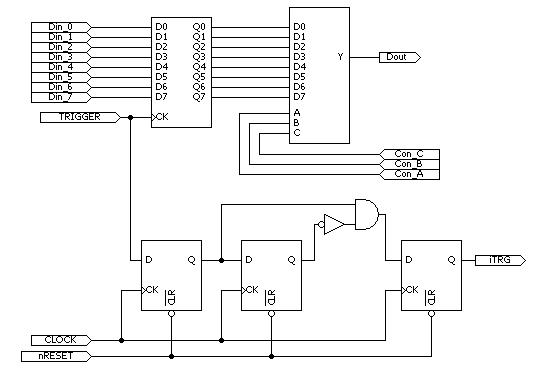

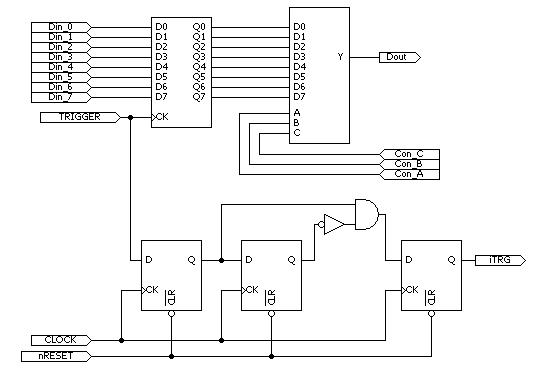

パラレルーシリアル変換器

入力バッファに、データセレクタを接続します。

Dout <= iREG( conv_integer( con ) ) ;

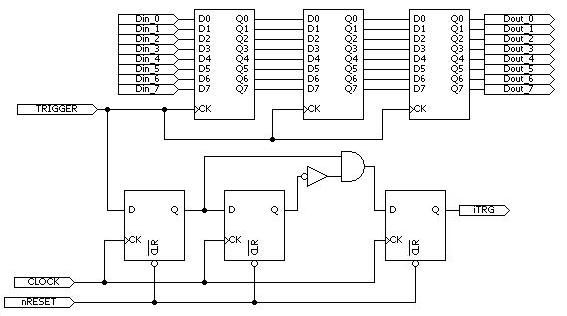

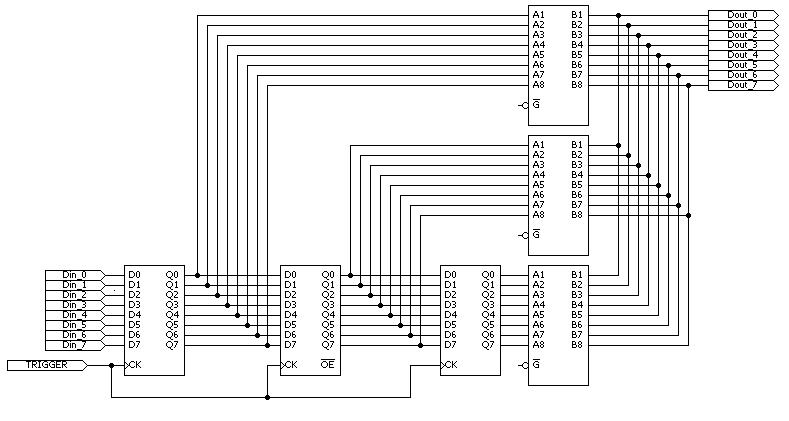

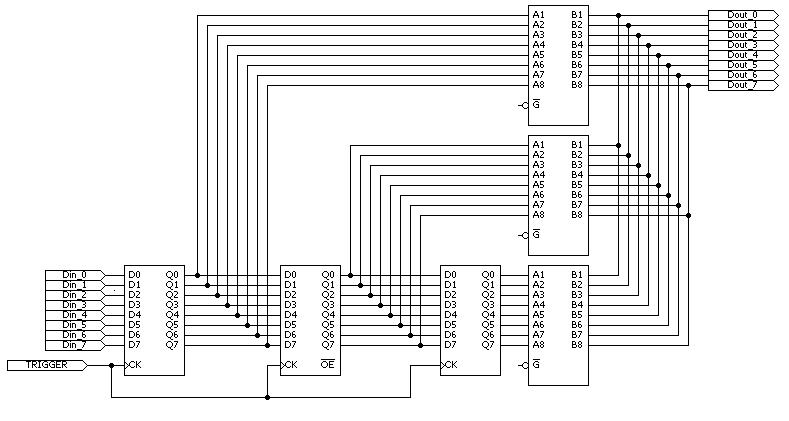

FIFO(First In First Out)

入力バッファを少し修正して、下図のようにレジスタを

並べて接続するとFIFOになります。

Dout <= iREG( conv_integer( con ) ) ;

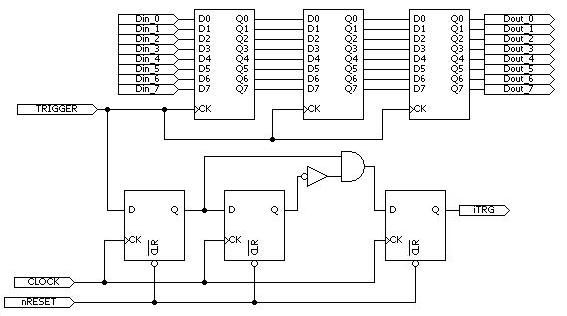

FIFO(First In First Out)

入力バッファを少し修正して、下図のようにレジスタを

並べて接続するとFIFOになります。

process( nRESET , TRIGGER )

begin

if ( nRESET = '0' ) then

iREG0 <= (others => '0') ;

iREG1 <= (others => '0') ;

iREG2 <= (others => '0') ;

elsif rising_edge( TRIGGER ) then

iREG0 <= iREG1 ;

iREG1 <= iREG2 ;

iREG2 <= Din ;

end if ;

end process;

Dout <= iREG ;

process( nRESET , CLOCK )

begin

if ( nRESET = '0' ) then

iSREG <= "00" ;

iTRG <= '0' ;

elsif rising_edge( CLOCK ) then

-- shift register

iSREG <= iSREG(0) & TRIGGER ;

-- judge

if ( iSREG = "01" ) then

iTRG <= '1' ;

else

iTRG <= '0' ;

end if ;

end if ;

end process;

LIFO(Last In First Out)

入力バッファに、データセレクタを接続して対応します。

process( nRESET , TRIGGER )

begin

if ( nRESET = '0' ) then

iREG0 <= (others => '0') ;

iREG1 <= (others => '0') ;

iREG2 <= (others => '0') ;

elsif rising_edge( TRIGGER ) then

iREG0 <= iREG1 ;

iREG1 <= iREG2 ;

iREG2 <= Din ;

end if ;

end process;

Dout <= iREG0 when( sel = "10" ) else

iREG1 when( sel = "01" ) else

iREG2 when( sel = "00" ) else

(others => '0');

この考え方を応用すると、指定の入力レジスタからデータを

引き出すことができます。

process( nRESET , TRIGGER )

begin

if ( nRESET = '0' ) then

iREG0 <= (others => '0') ;

iREG1 <= (others => '0') ;

iREG2 <= (others => '0') ;

elsif rising_edge( TRIGGER ) then

iREG0 <= iREG1 ;

iREG1 <= iREG2 ;

iREG2 <= Din ;

end if ;

end process;

Dout <= iREG ;

process( nRESET , CLOCK )

begin

if ( nRESET = '0' ) then

iSREG <= "00" ;

iTRG <= '0' ;

elsif rising_edge( CLOCK ) then

-- shift register

iSREG <= iSREG(0) & TRIGGER ;

-- judge

if ( iSREG = "01" ) then

iTRG <= '1' ;

else

iTRG <= '0' ;

end if ;

end if ;

end process;

LIFO(Last In First Out)

入力バッファに、データセレクタを接続して対応します。

process( nRESET , TRIGGER )

begin

if ( nRESET = '0' ) then

iREG0 <= (others => '0') ;

iREG1 <= (others => '0') ;

iREG2 <= (others => '0') ;

elsif rising_edge( TRIGGER ) then

iREG0 <= iREG1 ;

iREG1 <= iREG2 ;

iREG2 <= Din ;

end if ;

end process;

Dout <= iREG0 when( sel = "10" ) else

iREG1 when( sel = "01" ) else

iREG2 when( sel = "00" ) else

(others => '0');

この考え方を応用すると、指定の入力レジスタからデータを

引き出すことができます。

出力シンクロナイザ

出力シンクロナイザには、次のような種類があります。

- 出力バッファ

- シリアルーパラレル変換器

- パラレルーシリアル変換器

- FIFO(First In First Out)

言葉で表現すると3種類ですが、結局はレジスタ、シフト

レジスタ、データセレクタの組合せになります。

出力バッファ

レジスタ出力をそのまま出力するか、ハイインピーダンスで制御します。

Dout <= iREG when( iREAD = '0' ) else

(others => 'Z');

シリアルーパラレル変換器

シフトレジスタの出力をそのまま出力します。

Dout <= iREG when( iREAD = '0' ) else

(others => 'Z');

シリアルーパラレル変換器

シフトレジスタの出力をそのまま出力します。

パラレルーシリアル変換器

レジスタ出力にデータセレクタを接続し、外部から制御します。

パラレルーシリアル変換器

レジスタ出力にデータセレクタを接続し、外部から制御します。

Dout <= iREG( conv_integer( CON ) ) ;

Dout <= iREG( conv_integer( CON ) ) ;

目次

前

次

外部からデータが入力されたことを、RisingEdgeかFallingEdgeのトリガー

で捕捉して、内部回路に信号として伝達します。

process( nRESET , TRIGGER )

begin

if ( nRESET = '0' ) then

iREG <= (others => '0') ;

elsif rising_edge( TRIGGER ) then

iREG <= Din ;

end if ;

end process;

Dout <= iREG ;

process( nRESET , CLOCK )

begin

if ( nRESET = '0' ) then

iSREG <= "00" ;

elsif rising_edge( CLOCK ) then

-- shift register

iSREG <= iSREG(0) & TRIGGER ;

end if ;

end process;

-- judge

iTRG <= '1' when ( iSREG = "01" ) else '0' ;

シリアルーパラレル変換器

シリアル-パラレル変換は、シフトレジスタを用意しておき

外部トリガーでデータ入力とシフトを同時に実現します。

外部からデータが入力されたことを、RisingEdgeかFallingEdgeのトリガー

で捕捉して、内部回路に信号として伝達します。

process( nRESET , TRIGGER )

begin

if ( nRESET = '0' ) then

iREG <= (others => '0') ;

elsif rising_edge( TRIGGER ) then

iREG <= Din ;

end if ;

end process;

Dout <= iREG ;

process( nRESET , CLOCK )

begin

if ( nRESET = '0' ) then

iSREG <= "00" ;

elsif rising_edge( CLOCK ) then

-- shift register

iSREG <= iSREG(0) & TRIGGER ;

end if ;

end process;

-- judge

iTRG <= '1' when ( iSREG = "01" ) else '0' ;

シリアルーパラレル変換器

シリアル-パラレル変換は、シフトレジスタを用意しておき

外部トリガーでデータ入力とシフトを同時に実現します。

全データのセットが終了したかは、データ自体にフラグを用意して

LSBかMSBにつけておくか、もう一つシフトレジスタを用意し

内部回路に信号として伝達します。

process( nRESET , TRIGGER )

begin

if ( nRESET = '0' ) then

iREG <= "0000" ;

elsif rising_edge( TRIGGER ) then

iREG <= iREG(2 downto 0) & Din ;

end if ;

end process;

パラレルーシリアル変換器

入力バッファに、データセレクタを接続します。

全データのセットが終了したかは、データ自体にフラグを用意して

LSBかMSBにつけておくか、もう一つシフトレジスタを用意し

内部回路に信号として伝達します。

process( nRESET , TRIGGER )

begin

if ( nRESET = '0' ) then

iREG <= "0000" ;

elsif rising_edge( TRIGGER ) then

iREG <= iREG(2 downto 0) & Din ;

end if ;

end process;

パラレルーシリアル変換器

入力バッファに、データセレクタを接続します。

Dout <= iREG( conv_integer( con ) ) ;

FIFO(First In First Out)

入力バッファを少し修正して、下図のようにレジスタを

並べて接続するとFIFOになります。

Dout <= iREG( conv_integer( con ) ) ;

FIFO(First In First Out)

入力バッファを少し修正して、下図のようにレジスタを

並べて接続するとFIFOになります。

process( nRESET , TRIGGER )

begin

if ( nRESET = '0' ) then

iREG0 <= (others => '0') ;

iREG1 <= (others => '0') ;

iREG2 <= (others => '0') ;

elsif rising_edge( TRIGGER ) then

iREG0 <= iREG1 ;

iREG1 <= iREG2 ;

iREG2 <= Din ;

end if ;

end process;

Dout <= iREG ;

process( nRESET , CLOCK )

begin

if ( nRESET = '0' ) then

iSREG <= "00" ;

iTRG <= '0' ;

elsif rising_edge( CLOCK ) then

-- shift register

iSREG <= iSREG(0) & TRIGGER ;

-- judge

if ( iSREG = "01" ) then

iTRG <= '1' ;

else

iTRG <= '0' ;

end if ;

end if ;

end process;

LIFO(Last In First Out)

入力バッファに、データセレクタを接続して対応します。

process( nRESET , TRIGGER )

begin

if ( nRESET = '0' ) then

iREG0 <= (others => '0') ;

iREG1 <= (others => '0') ;

iREG2 <= (others => '0') ;

elsif rising_edge( TRIGGER ) then

iREG0 <= iREG1 ;

iREG1 <= iREG2 ;

iREG2 <= Din ;

end if ;

end process;

Dout <= iREG0 when( sel = "10" ) else

iREG1 when( sel = "01" ) else

iREG2 when( sel = "00" ) else

(others => '0');

この考え方を応用すると、指定の入力レジスタからデータを

引き出すことができます。

process( nRESET , TRIGGER )

begin

if ( nRESET = '0' ) then

iREG0 <= (others => '0') ;

iREG1 <= (others => '0') ;

iREG2 <= (others => '0') ;

elsif rising_edge( TRIGGER ) then

iREG0 <= iREG1 ;

iREG1 <= iREG2 ;

iREG2 <= Din ;

end if ;

end process;

Dout <= iREG ;

process( nRESET , CLOCK )

begin

if ( nRESET = '0' ) then

iSREG <= "00" ;

iTRG <= '0' ;

elsif rising_edge( CLOCK ) then

-- shift register

iSREG <= iSREG(0) & TRIGGER ;

-- judge

if ( iSREG = "01" ) then

iTRG <= '1' ;

else

iTRG <= '0' ;

end if ;

end if ;

end process;

LIFO(Last In First Out)

入力バッファに、データセレクタを接続して対応します。

process( nRESET , TRIGGER )

begin

if ( nRESET = '0' ) then

iREG0 <= (others => '0') ;

iREG1 <= (others => '0') ;

iREG2 <= (others => '0') ;

elsif rising_edge( TRIGGER ) then

iREG0 <= iREG1 ;

iREG1 <= iREG2 ;

iREG2 <= Din ;

end if ;

end process;

Dout <= iREG0 when( sel = "10" ) else

iREG1 when( sel = "01" ) else

iREG2 when( sel = "00" ) else

(others => '0');

この考え方を応用すると、指定の入力レジスタからデータを

引き出すことができます。

Dout <= iREG when( iREAD = '0' ) else

(others => 'Z');

シリアルーパラレル変換器

シフトレジスタの出力をそのまま出力します。

Dout <= iREG when( iREAD = '0' ) else

(others => 'Z');

シリアルーパラレル変換器

シフトレジスタの出力をそのまま出力します。

パラレルーシリアル変換器

レジスタ出力にデータセレクタを接続し、外部から制御します。

パラレルーシリアル変換器

レジスタ出力にデータセレクタを接続し、外部から制御します。

Dout <= iREG( conv_integer( CON ) ) ;

Dout <= iREG( conv_integer( CON ) ) ;